### 연구논문

# Sn-Pb 공정솔더 플립칩의 접합강도에 미치는 플라즈마 처리 효과

홍 순 민\*·강 춘 식\*\*·정 재 필\*\*\*

\*(주)삼성전자 메카트로닉스센터 지능시스템연구소 마이크로접합 Lab.

\*\*서울대학교 재료공학부

\*\*\*\*서울시립대학교 재료공학과

## Effect of Plasma Treatment on the Bond Strength of Sn-Pb Eutectic Solder Flip Chip

Soon-Min Hong\*, Choon-Sik Kang\*\* and Jae-Pil Jung\*\*\*

\*Micro-joining Lab., Institute of Intelligent system, Mechatronics Center, Samsung Electronics Co. Ltd., 416 Metan-3Dong, Paldal-Gu, Suwon City, Kyungki-Do, 442-742, Korea

\*\*School of Materials Science & Engineering, Seoul National University, Seoul 151-744, Korea

\*\*\*Department of Materials Science & Engineering, University of Seoul, Seoul 130-743, Korea

#### Abstract

Fluxless flip chip bonding process using plasma treatment instead of flux was investigated. The effect of plasma process parameters on tin-oxide etching characteristics were estimated with Auger depth profile analysis. The die shear test was performed to evaluate the adhesion strength of the flip chip bonded after plasma treatment. The thickness of oxide layer on tin surface was reduced after Ar+H<sub>2</sub> plasma treatment. The addition of H<sub>2</sub> improved the oxide etching characteristics by plasma. The die shear strength of the plasma-treated Sn-Pb solder flip chip was higher than that of non-treated one but lower than that of fluxed one. The difference of the strength between plasma-treated specimen and non-treated one increased with increase in bonding temperature. The plasma-treated flip chip fractured at solder/TSM interface at low bonding temperature while the fracture occurred at solder/UBM interface at higher bonding temperature.

(Received December 10, 2001)

Key Words: Flip chip, Solder, Plasma, Fluxless, Shear strength, Oxide layer

## 1. 서 론

솔더 범프를 이용한 플립칩 패키지 기술은 실장밀도를 증가 시킬 수 있는 궁극적인 방법으로서, 다수의 미세피치 I/O 단자를 갖는 전자 부품의 연결에 사용이증가하고 있다. 솔더 범프 플립칩 기술은 높은 수율과 신뢰성 있는 접합 기술임이 이미 증명되었으며 그 응용범위를 광전자소자 및 MEMS (Microelectromechanical system) 부품의 실장에까지 확장하고 있다<sup>1)</sup>.

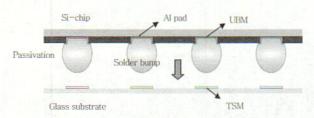

Fig. 1은 flip chip on glass 패키지 시스템의 개략 도를 나타낸다. 일반적인 솔더 플립칩 패키지 공정에서 는 솔더 범핑과 플립칩 접합의 두가지 공정에 플릭스가 사용된다. 현재 패키지 산업에서 주로 사용되고 있는 범핑 기술에는 열증착, 전해도금, 스텐실 프린팅, 솔더스터드 와이어 범핑 등이 있다. 이러한 기술들에서는 솔더를 칩상에 정의된 UBM (Under Bump Metallurgy)<sup>2)</sup> 패턴에 증착, 도금 혹은 도포한 후 플럭스를 바르고 리플로우하여 균일한 조성과 높이를 갖는 구형의 솔더 범프를 형성한다.

플릭스를 사용하는 또 다른 공정은 플립칩 접합 공정이다. 기존의 tacky flux 공정에서는 플릭스를 솔더 범프에 바르고 플립칩을 기판의 TSM (Top Surface Metallurgy)<sup>3)</sup> 패드 위에 정렬시켜 놓은 후에 리플로우를 거쳐 접합한다.

그러나, 미세피치 플립칩 패키지 공정에 플럭스를 사용할 경우, 잔류 플럭스가 검사나 세정이 불가능한 곳에 잔존할 수 있다<sup>4)</sup>. 전자 부품에 잔류한 플럭스는 미

Fig. 1 Si-chip on glass flip-chip bonding system

세회로의 부식을 일으킬 수 있으며 장기간에 걸쳐 제품의 신뢰성에 악영향을 미칠 우려가 있다<sup>5)</sup>. 게다가, 플릭스 세정 용매들이 환경에 유해함이 밝혀지면서 몬트리올 규약과 교토 규약과 같이 오존층을 파괴하고 지구온난화를 일으키는 용매나 기체의 사용에 대한 규제가가속화되고 있다. 따라서, 플릭스의 사용을 대체할 새로운 공정이 필요하며, 이에 따라 무플릭스 플립칩 솔더링에 대한 연구가 활발하게 이루어지고 있다.

무플럭스 솔더링의 수단으로서  $CF_4^{(6)}$  혹은  $SF_6^{(7)}$  기체의 플라즈마나 카르복시산과 같은 유기산 증기(acid vapor)<sup>8)</sup>를 이용한 연구가 몇몇 연구 그룹에 의하여 진행되고 있다. 그러나, 불소는 플립칩 패키지의 패시배이션(passivation)으로 사용되는  $SiO_2$  와  $SiN_x$ 를 식각하는 성질이 있음이 밝혀졌다. 또한, 유기산 증기를 이용하는 기술은 공정 후 폐가스를 정제해야 하는 문제점이 있다<sup>9)</sup>.

본 연구에서는 환경에 유해함이 증명된  $CF_4$ 과  $SF_6$  기체 보다 환경 친화적인  $Ar^{10}$ 과  $H_2$  를 공정 기체로 하는 플라즈마를 사용하여 Sn-Pb 솔더가 범핑된 플립칩 패키지를 사용하지 않고 접합하고자 하였다. 플라즈마 공정 변수가 솔더의 산화막 식각 특성에 미치는 영향을 평가하였고 플라즈마 처리하여 접합한 플립칩과 플릭스를 사용한 플립칩의 전단강도와 플릭스를 사용하여 접합한 플립칩의 전단강도를 비교함으로써 무플릭스 플립칩 접합 수단으로서  $Ar+H_2$  플라즈마 처리의 응용가능성에 대하여 검토하였다.

## 2. 실험방법

## 2.1 산화막의 Auger 전자 분석

솔더 표면의 산화막 식각에 미치는 플라즈마 처리의 영향을 평가하기 위하여 Sn. 솔더 디스크의 표면을 다양한 조건에서 플라즈마 처리한 후에 AES (Auger Electron Spectroscopy) depth profile 분석을 하였다. Sn-Pb 솔더의 경우 솔더 표면의 산화막은 대부분 Sn의 산화막이므로 순수한 Sn. 솔더를 압연하여 범프의 높이와 같은 수준인 100㎞ 두께로 압연한 후에 편칭작업을 거쳐 직경 6mm의 디스크로 제조하였다. 솔더

디스크는 Cr 70nm/Cu 500nm/ Au 50nm UBM이 6.5mm 직경의 원형 패턴으로 증착되어 있는 Si-웨이퍼 위에서 리플로우되었다. 리플로우는 대기중에서 핫플레이트(hot plate)에서 수행하였으며, 250°C 에서 2분간 리플로우하여 솔더 표면에 산화막이 성장하도록하였다. Auger 분석은 산화막의 식각속도를 7nm/min의 속도로 스퍼터링(sputtering)하면서 O, C, Sn 원소들의 함량을 분석하였다.

#### 2.2 플라즈마 처리조건

플라즈마 처리는 13.56MHz의 RF 플라즈마 식각장비를 사용하였다. 플라즈마 기체로는 Ar과 H<sub>2</sub>의 혼합기체를 사용하였으며 H<sub>2</sub> 기체의 조성을 0~20% 범위에서 혼합하였다. Sn 솔더 디스크의 경우 250mTorr의 Ar 플라즈마에서 50W에서 약 170초 후에 플라즈마의 열에 의해 용융되었다. 따라서, 플라즈마 처리는 솔더가 용융되지 않는 10~50W출력범위에서 10~120s의 시간범위에서 수행하였다. 작업 공간의 진공을 5mTorr까지 뽑은 후에 플라즈마 기체를 흘려주고 압력을 100~400mTorr의 범위로 유지시킨 후에 플라즈마 처리를 하였다. 플라즈마 공정 변수로는 H<sub>2</sub> 기체의 첨가량, 플라즈마의 출력과 처리시간으로 하였다

### 2.3 플라즈마 처리후 플립칩의 무플럭스 접합

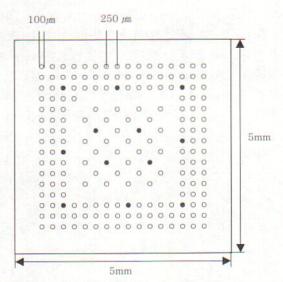

플립칩 UBM 패턴과 접합시험을 위하여 100μm 직경의 원형 Cr 70nm/Cu 300nm/Cu 4μm/Ni 4μm UBM 패드가 패터닝된 5mm x 5mm 크기의 실리콘 다이를 제작하였다. UBM은 실리콘 웨이퍼에 Cr 70nm/Cu 300nm 층을 도금 씨앗층(seed layer)으로 진공증착하였으며, 여기에 Cu 4μm/Ni 4μm을 전해도금으로 증착하였다. 시험용 다이에 부분적으로 12개의 Sn-Pb 솔더범프의 범평하였으며 그 위치를 Fig. 2에 나타내었다. 솔더범프의 범평하였으며 그 위치를 Fig. 2에 나타내었다. 솔더범프는 100μm 직경의 Sn-37mass%Pb 솔더볼을 레이저볼접합 공정을 사용하여 Cu/Ni UBM에 초기접합한후에 VOC(Volatile Organic Compound)-free flux를 도포한 후 210℃에서 10초간 리플로우하였다. 리플로우 후 범프의 높이는 약 70μm이었고 범프의 전단강도는 60~70g~force이었다.

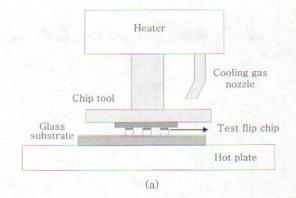

리플로우 후 12 곳에 범핑된 시험용 실리콘 다이를 플라즈마 처리한 후에 Fig. 3(a)에 도시된 플립칩 본 더를 사용하여 Cr 70nm/Cu 1 $\mu$ m/Au 100nm가 TSM 으로 증착되어 있는 유리기판에 접합하였다. 플립칩 본 더는 진공으로 플립칩을 집어올려 기판상의 원하는 위치에 정렬하여 위치시키고, 칩을 잡고있는 칩툴(chip

Fig. 2 Test chip for fluxless bonding by plasma treatment. The closed circles are 12bumps positions on Si-die for flip chip bonding

tool)과 기판을 바치고 있는 핫플레이트를 동시에 가열하여 플립칩을 기판에 접합시키는 장비이다. 접합 온도는 Sn-Pb의 경우 190, 200, 210℃ 를 최고점 온도로 하여 접합하였으며, Fig. 3(b)와 같은 온도 프로파일 조건에서 접합하였다. 이때, 칩툴과 핫플레이트의최고점 온도를 같게 하여 접합하였다. 플라즈마 처리는 Ar+10%H₂ 플라즈마를 사용하여 50W 출력조건에서 40초간 플라즈마 처리를 하였다. 플라즈마 처리후 2시간 이내에 유리기판과 접합하였다.

유리기판에 접합된 실리콘 다이(die)에 대하여 다이 전단시험(die shear test)을 행하였다. 5mm×5mm 다이의 한쪽 모서리를 전단도구로 밀었으며 이때 전단도구의 높이는 유리기판으로부터 100μm 이고 전단속도는 200μm/s로 하였다. 전단시험 후 실리콘 다이쪽과 유리기판 쪽의 파단면을 SEM으로 분석하였다. 플라즈마 처리 후 접합한 시편의 전단강도를 아무런 처리도하지 않고 접합한 시편, VOC-free flux를 사용하여 접합한 시편의 전단강도와 비교하였다.

#### 3. 실험 결과 및 고찰

## 3.1 Sn 표면 산화막의 식각에 미치는 플라즈마 처리 공정변수의 영향

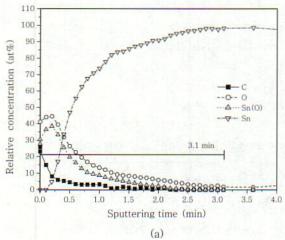

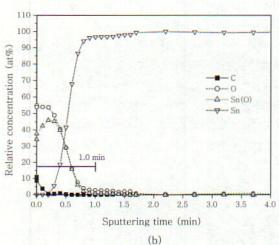

플라즈마 처리가 솔더 표면의 산화막 제거에 미치는 영향을 평가하기 위하여 UBM이 증착된 Si-웨이퍼 위 에서 리플로우된 Sn 디스크 표면의 산화막을 AES depth profile로 분석하였다. Fig. 4(a)와 (b)는 Sn 솔더에 대하여 Ar+10%H<sub>2</sub> 기체를 사용하여 50W에서

Fig. 3 Flip chip bonding system. (a) Schematics of flip chip bonding using heatable chip tool (b) Temperature profile for Sn-37mass%Pb solder bumped flip chip bonding after plasma treatment

60초간의 플라즈마 처리 전·후의 AES 분석결과를 각각 나타낸다. Sn 솔더의 경우 O와 Sn(O)가 검출되지않을 때까지 걸리는 스퍼터링 시간이 3.1분인데 비하여 플라즈마 처리 후에는 1분으로 감소하였음을 알 수 있다. AES 식각속도가 SiO2를 기준으로 측정된 것이지만 식각 속도가 일정할 경우 식각된 두께는 시간에 비례하므로 Sn 솔더의 경우 약 3배정도 산화막이 얇아졌다고 판단할 수 있다. Sn의 산화물은 SnO와 SnO2가 있으며 이들의 생성자유에너지는 각각 515.0, -515.8 kJ/mole로 거의 비슷하므로 열역학적으로 둘다 Sn의 안정한 산화막이 될 수 있으며, 다만 산화시의 속도론적 변수에 따라 SnO와 SnO2의 생성이 결정된다. 그러나, 이러한 속도론적 환경도 엄밀하게 결정되기 힘들며일반적으로 Sn의 산화막은 SnO와 SnO2의 혼합물 상태로 된 것으로 여겨지고 있다<sup>11)</sup>.

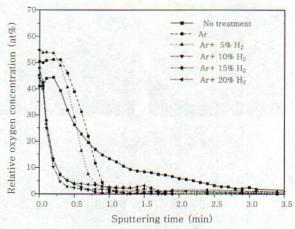

Fig. 5는 50W, 30초의 동일한 플라즈마 처리 조건 하에서 플라즈마 기체의 조성을 Ar과  $0\sim20\%H_2$ 로 변 화시키면서 Sn 솔더 표면의 산화막을 식각하였을 때 Auger 분석결과를 보여준다. Fig. 5에서 Ar gas만 사

Fig. 4 AES depth profile of Sn solder after plasma before and after plasma treatment. (The etch rate is 7nm/min for SiO<sub>2</sub>.) (a) Before plasma treatment. (b) After Ar+10%H<sub>2</sub> plasma treatment at 50W for 60s.

용하는 경우보다  $H_2$ 를 첨가하는 경우 산화막 식각이보다 효과적으로 이루어짐을 관찰할 수 있다.  $H_2$ 는 플라즈마 중에서 해리되어 단원자  $H^+$  이온이 되며, 이것이 산화물을 환원시키는 역할을 한다<sup>12)</sup>. 그러나  $H_2$ 가  $10\%\sim20\%$ 까지는 산화막의 식각 효과가 거의 비슷함을 알 수 있다. 따라서  $H_2$ 의 양을 10%정도만 첨가하여도 효과적으로  $S_1$  산화막을 제거할 수 있을 것으로 판단된다.

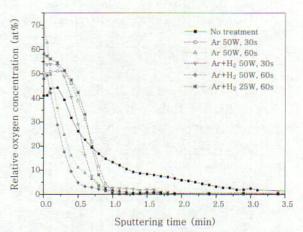

Fig. 6은 동일한 압력조건에서 출력과 처리시간을 변경하면서 플라즈마 처리를 한 Sn 시편의 AES 분석 결과이다. 그림에서 Ar 플라즈마 보다는 Ar+H<sub>2</sub> 플라즈마가 산화막 식각성능이 우수하고, 플라즈마의 출력이 높을수록, 플라즈마 처리시간이 길수록 산화막의 식각이 잘 이루어짐을 관찰 할 수 있다. 하지만, 50W, 250mTorr의 압력에서 Sn 솔더 디스크는 약 170초 후에 플라즈마의 열에 의하여 용융이 됨을 관찰할 수 있

Fig. 5 Oxygen concentration of Sn surface etched by Ar+H<sub>2</sub> plasma with different H<sub>2</sub> content. ( Power: 50W, Time: 30s, Pressure: 270mTorr)

Fig. 6 Oxygen concentration of Sn surface etched by Ar+10%H<sub>2</sub> plasma with different power and time. (Pressure: 270mTorr)

었다. 따라서, 플라즈마에 의한 산화막의 식각은  $10\sim50$ W의 출력조건에서  $10\sim120$ s의 처리시간 내에서 이루어져야 솔더의 용융을 방지할 수 있었다.

## 3.2 플라즈마 처리 후 Sn-Pb 솔더 플립칩의 무플럭스 접합

Fig. 2와 같이 5mm×5mm 실리콘 다이의 12곳에 100μm 직경의 범프를 형성한 후 플립칩 본더를 사용하여 Cr 70nm/Cu 1μm/Au 100nm이 TSM으로 증착되어 있는 유리기판에 접합한 후 다이전단시험을 행하였다. 측정된 최대강도를 12로 나누어 범프 한 개당 전단 강도를 구하였다.

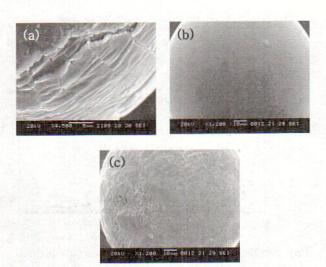

Fig. 7에 여러가지 공정을 거친 Sn-3.5Ag 솔더 범 프의 표면사진을 나타내었다. (a)는 230°C의 핫플레이 트에서 2분 동안 플럭스 없이 리플로우하여 표면 산화 막을 인위적으로 키운 것이다. 산화막이 솔더 표면에

Fig. 7 Sn-3.5mass%Ag Solder bump surface after different treatment (a) After reflow on hot plate at 230℃ for 2min without flux (b) After reflow with flux on hotplate at 250℃ for 10s (c) After Ar+10%H₂ plasma treatment at 50W for 60s

주름져 있음을 관찰할 수 있다. (b)는 플럭스를 범프에 바른 후 250℃에서 10초 동안 리플로우한 후의 표면사진으로 표면 산화막이 제거되어 매끈한 표면으로 됨을 볼 수 있다. (c)는 Ar+10%H₂ 플라즈마에 의하여 처리된 솔더 범프의 표면사진으로 산화막이 식각되고 표면 솔더의 일부도 식각되어 표면이 거칠어진 모습을 관찰할 수 있다.

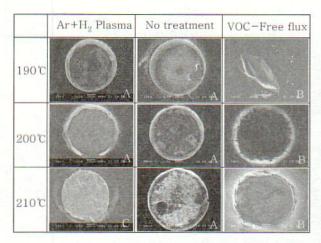

Fig. 8에 Sn-37mass%Pb 솔더가 범핑된 플립칩에 대한 전단시험 결과를 도시하였다. 플라즈마 처리를 하지 않은 시편과 VOC-free flux를 사용한 시편도 동일한

Fig. 8 Shear strength per bump from die shear test of Sn-37mass%Pb solder bumped flip chip with different pre-treatment before flip chip bonding.

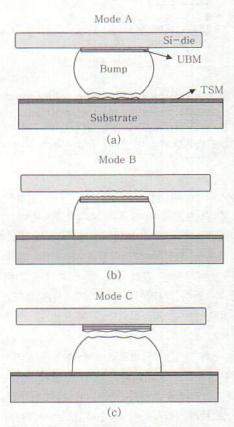

조건에서 접합하여 강도의 차이를 비교하였다. Fig. 8 에서 플라즈마 처리를 한 후 접합한 시편은 플라즈마처리를 하지 않은 시편보다 접합강도가 높지만 플럭스를 사용한 시편보다는 강도가 낮다는 것을 알 수 있다. 또한, 접합온도가 증가할수록 플라즈마처리된 시편과처리되지 않은 시편의 강도차이는 더욱 커짐을 관찰할수 있다. 다이전단시험 후 SEM으로 파면을 관찰하였으며 파단의 유형을 Fig. 9와 같이 분류하였다.

A형은 유리기판의 TSM과 솔더의 접합계면에서 일어 나는 파단을 나타내고, B형은 UBM과 실리콘 다이 접합 계면에서의 파단을 나타내며, C형은 솔더와 실리콘 다이의 UBM계면에서의 파괴를 나타낸다. B형이나 C형의 파괴 양상은 유리기판과 솔더와의 접합부가 양호함을 반증하며, 단지 UBM과 실리콘 다이의 접합강도와 솔더와 UBM의 접합강도에 따라 B형 혹은 C형의파괴양상으로 구분된다.

Fig. 10은 Sn-Pb 솔더가 범핑된 실리콘 다이쪽의 파괴 양상의 사진을 나타낸다. 플라즈마 처리를 한 시 편과 처리를 하지 않은 시편의 경우 190℃ 와 200℃ 의 접합온도에서 접합한 경우 대부분 A형의 파괴양상

Fig. 9 Fracture mode of the die shear test specimen (a) Interface between solder and TSM of glass substrate (b) Interface between UBM and Si-wafer (c) Interface between solder and UBM of Si-wafer

Fig. 10 Fracture surface of Sn-37mass%Pb bumped die bonded to glass substrate after die shear test. (Si-die side)

을 보였다. 그러나 210℃의 접합온도에서 플라즈마 처리한 시편은 B형을, 플라즈마 처리를 하지 않은 시편은 A형의 파괴양상을 보였다. 따라서, Sn-Pb의 경우 접합온도가 높을수록 플라즈마 처리를 한 시편과 플라즈마 처리하지 않은 시편의 접합 강도차이가 커짐을 알수 있다. 플릭스를 사용한 후 접합한 시편의 경우 파괴양상은 거의 B형의 양상을 보였으며 이것은 솔더와 유리기판의 접합이 양호함을 나타낸다.

플럭스를 사용한 시편은 모든 접합온도에서 양호한 접합을 이름을 알 수 있었다. 플라즈마 처리를 한 시편과 플라즈마 처리를 하지 않은 시편의 강도와 파괴양상은 낮은 온도에서는 거의 차이가 나지 않았지만 솔더의 융점에서 30℃ 이상 높은 온도에서는 플라즈마 처리한 시편이 강도와 파괴양상 면에서 플라즈마 처리를 하지 않은 시편보다 접합부가 우수함을 알 수 있었다.

플라즈마 처리를 한 시편은 산화막의 두께가 감소되고, 이로 인하여 솔더 용융시에 부피 팽창으로 얇은 산화막이 파괴되면서 용융된 솔더가 유리기판의 TSM과 접합이 이루어 지므로 플라즈마 처리를 하지 않은 시편보다는 강도가 높다고 할 수 있다. 본 연구에서는 대기중에서 플립칩 접합을 하였다. 플릭스를 사용한 시편의경우는 접합부를 덮고 있는 플릭스가 산화막을 제거함과 동시에 용융 솔더의 재산화를 방지하는 역할을 한다. 그러나, 플라즈마 처리한 시편은 온도가 가열됨에따라 산화막을 뚫고 나온 용융 솔더가 대기와 접하여재산화되므로 플릭스를 사용한 시편보다 접합강도가 떨어진다고 판단된다. 따라서 플라즈마 처리후 접합하는경우 대기 분위기보다는 질소 분위기<sup>13)</sup>에서 접합공정을수행한다면 플릭스를 사용하여 접합한 시편과의 강도차이를 보다 줄일 수 있을 것이라고 생각된다.

### 4. 결 론

플라즈마 처리를 이용한 Sn-Pb 솔더 플립칩의 무플럭스 접합에 대한 연구에서 다음과 같은 결론을 내릴 수 있었다.

- 1)  $Ar + H_2$  플라즈마 처리에 의하여 Sn 표면 산화막의 두께를 줄일 수 있었으며 이때  $H_2$ 의 첨가에 의하여 산화막 식각 특성이 향상되었으나 10%이상  $H_2$ 를 첨가할 때 식각 특성의 향상효과가 감소하였다.

- 2) 플라즈마 처리후 접합된 플립칩의 전단강도는 플라즈마 처리하지 않은 시편보다는 우수하였지만 플럭스를 사용하여 접합된 시편의 강도보다는 낮았다. 또한, 접합온도가 증가할수록 플라즈마 처리하지 않은 시편과의 강도차이가 더욱 증가하였다.

- 3) 플릭스를 사용하여 접합한 플립칩의 파괴는 주로 실리콘 다이와 UBM의 계면에서 발생하였으며 플라즈 마 처리하지 않은 시편의 파괴는 주로 솔더 범프와 유 리기판의 TSM에서 발생하였다. 플라즈마 처리한 시편 의 파괴는 저온의 접합온도에서는 솔더범프와 TSM에 서 일어났지만 고온의 접합온도에서는 UBM과 실리콘 다이 계면 혹은 UBM과 솔더 범프계면에서 파괴가 발 생하였다.

## 참 고 문 헌

- R. R. Tummala: Fundamentals of Microsystems Packaging, McGrow-Hill, New York, (2000), 544

- S. M. Hong, J. Y. Park, J. P. Jung and C. S. Kang: Fluxless Wetting Properties of One side-Coated Under Bump Metallurgy and Top Surface Metallurgy, J. Elec. Mater. 30-3(2001), 520-527

- S. M. Hong, J. Y. Park, J. P. Jung and C. S. Kang: Fluxless Wetting Properties of Top Surface Metallurgy in Different Pb-free Solders, Mater. Trans. 42-7(2001), 1423-1427

- C. Beddingfield and L. M. Higgins: The Effects of Flux Materials on the Moisture Sensitivity and Reliability of Flip-Chip-on-Board Assemblies, IEEE Transactions on CPMT Part C, 21(1998), 189-195.

- M. Bixenaman and E. Miller: Pro. 5th Int. Joint Symp. on Microelec. and Packaging, (IMAPS-KOREA and IEEE-CPMT, Seoul, Korea) (2000), 43-55

- K. J. Wolter, Th. Zerna, R. Deltschew, and H. Neumann: Plasma Treatment Process for Fluxless Reflow Soldering, 2001 IEEE-ETCT Conference Proceeding, (2001), 1295-1298

- N. Koopman, S. Bobbio, S. Nangalia, J. Bousaba, and B. Piekarski: Fluxless Soldering in Air and Nitrogen, 1993 IEEE-ECTC Conference Proceeding, (1993), 595-605

- 8. H. Matsuki, H. Matsui, and E. Watanabe: Fluxless

- Bump Reflow Using Carboxylic Acid, Proceeding of 2001 Intl Symposium on Advanced Packaging Materials, (2001), 135-139

- F. Masahiko, M. Tsugunori, D. Kazuhide, N. Hiroshi: Flux Free Flip Chip Attach Technology for BGA/CSP Packages, 1999 IEEE-ECTC Conference Proceeding, (1999), 408-414

- C. B. Park, S. M. Hong, J. P. Jung, C. S. Kang and Y. E. Shin: A Study on the Fluxless Soldering of Si-wafer/Glass Substrate Using Sn-3.5mass%Ag and Sn-37mass%Pb Solder, Mater. Trans., 42-7 (2001), 820-824

- D. M. Tench: Oxidation of Solder Coating, The Mechanics of Solder Alloy Wetting and Spreading ed. by F. G. Yost, F. M. Hosking, D. R. Frear, Van Nostrand Reinhold, New York, (1993), 163

- C. A. Mackay: Fluxes and Flux Action, The Mechanics of Solder Alloy Wetting and Spreading ed. by F. G. Yost, F. M. Hosking, D. R. Frear, Van Nostrand Reinhold, New York, (1993), 85

- S. M. Hong, J. Y. Park, J. P. Jung and C. S. Kang: Fluxless Wetting Properties of the UBM-coated Si-wafer to Pb-free Solders under Different Atmosphere, Mater. Trans., 42-3(2001), 520-527