1. Introduction

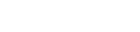

Fig.┬Ā1

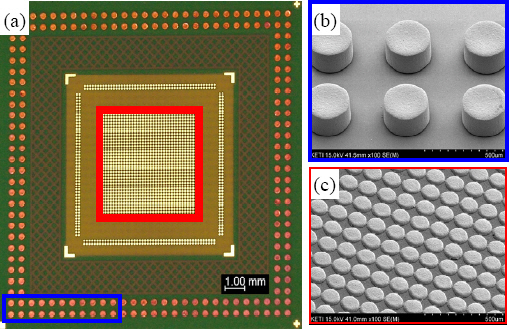

Fig.┬Ā2

Fig.┬Ā3

Fig.┬Ā4

2. Experiment Method

2.1 Used Materials

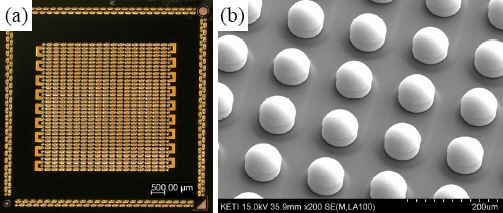

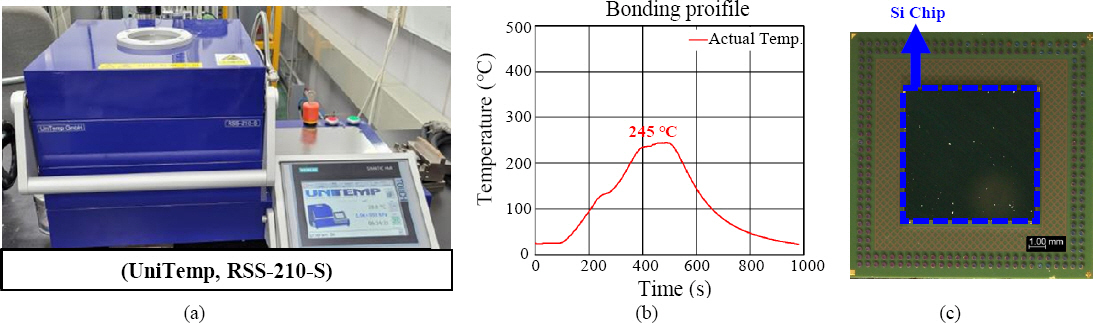

2.2 Thermal compression bonding (TC bonding)

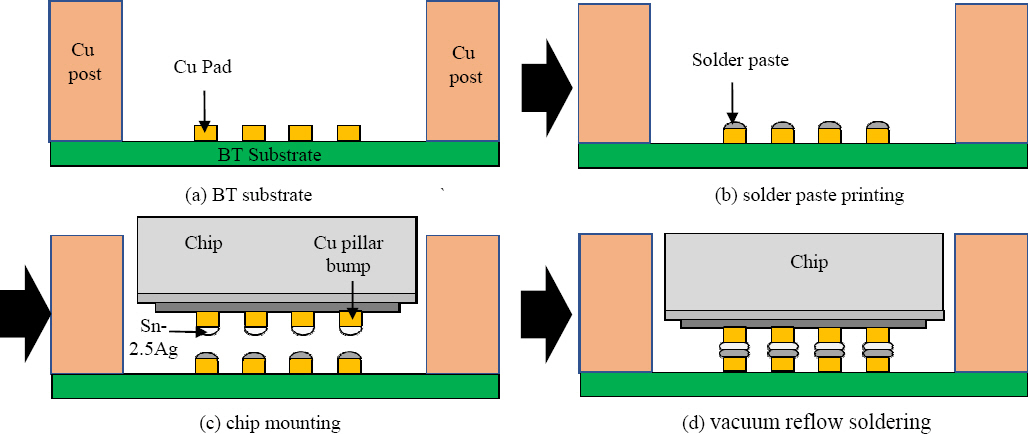

2.3 Vacuum reflow soldering (VR soldering)

2.4 Measurement of solder joint void content and cross-sectional analysis

2.5 Measurement of solder joint IMC thickness and area fraction

(1)

3. Experimental Results and Discussion

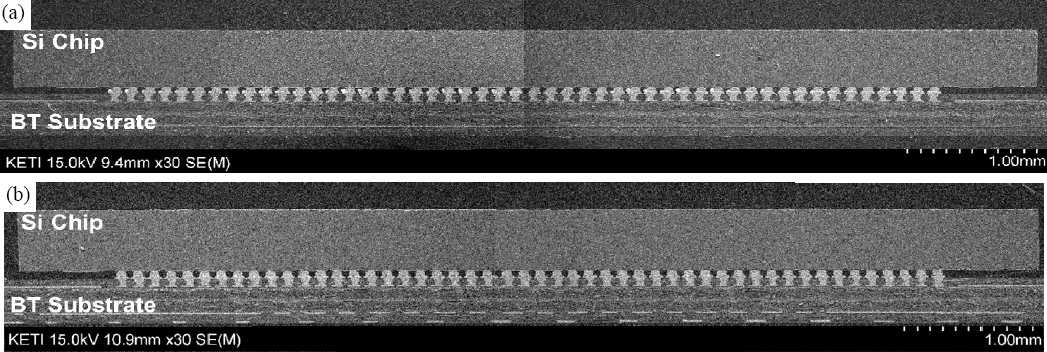

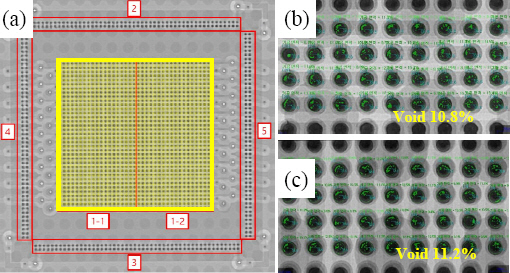

3.1 Analysis of solder joint void

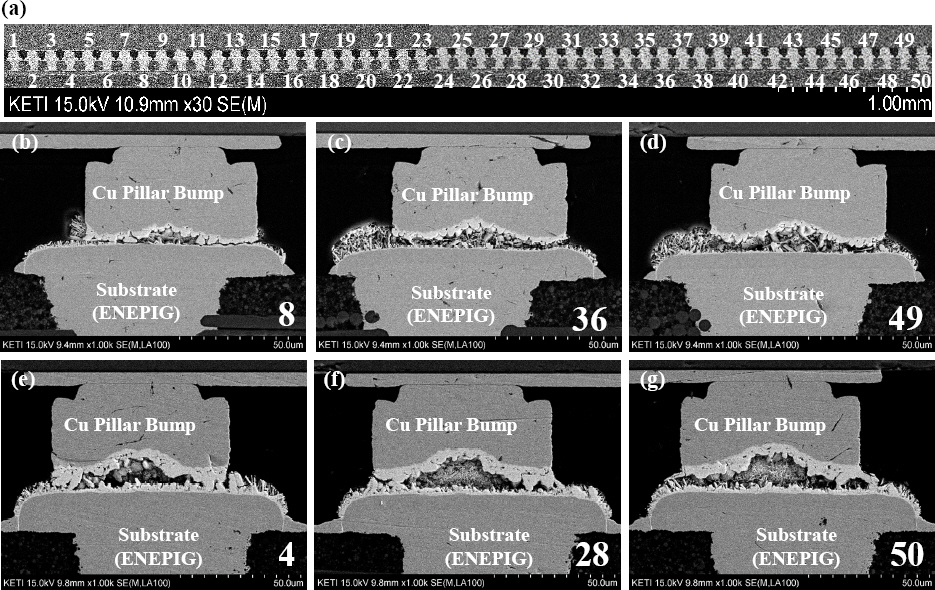

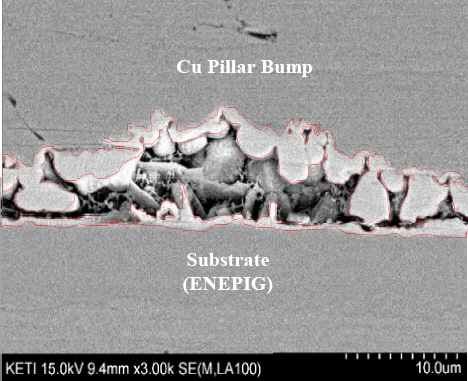

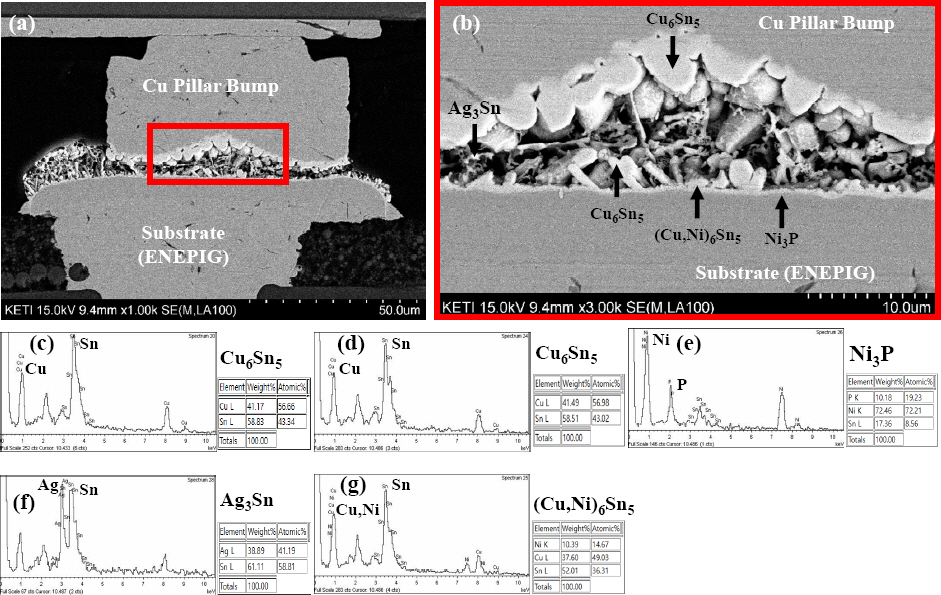

3.2 Cross-sectional microstructural analysis of solder joints

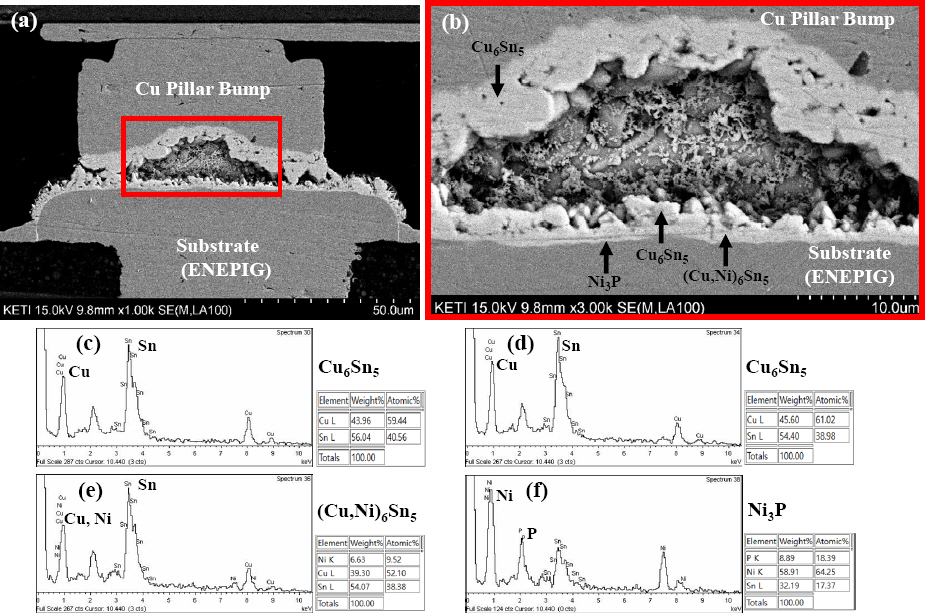

Fig.┬Ā11

Fig.┬Ā12

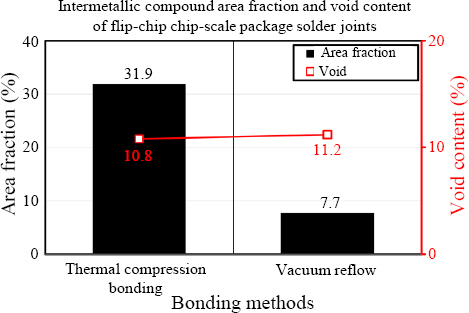

3.3 Analysis of IMC thickness and area fraction of solder joints

Table┬Ā1

4. Conclusions

1) The solder joint void content of the TC and VR process samples was 10.8% and 11.2%, respectively. It is thought that the voids in the TC process were caused by the pressurization during processing and the vacuum atmosphere in the VR process.

2) The joint area of the chip was thinner because the TC process pressurized the bumps on the chip at a high pressure to reliably bond them. Consequently, the IMC area fraction of the solder joint of the Cu pillar bump was smaller for the VR process sample than for the TC process sample.

3) The above results suggest that the VR process in a formic acid atmosphere can achieve simultaneous bonding of passive devices and Si chips with a 130 ŃÄø bump pitch.

PDF Links

PDF Links PubReader

PubReader ePub Link

ePub Link Full text via DOI

Full text via DOI Download Citation

Download Citation Print

Print